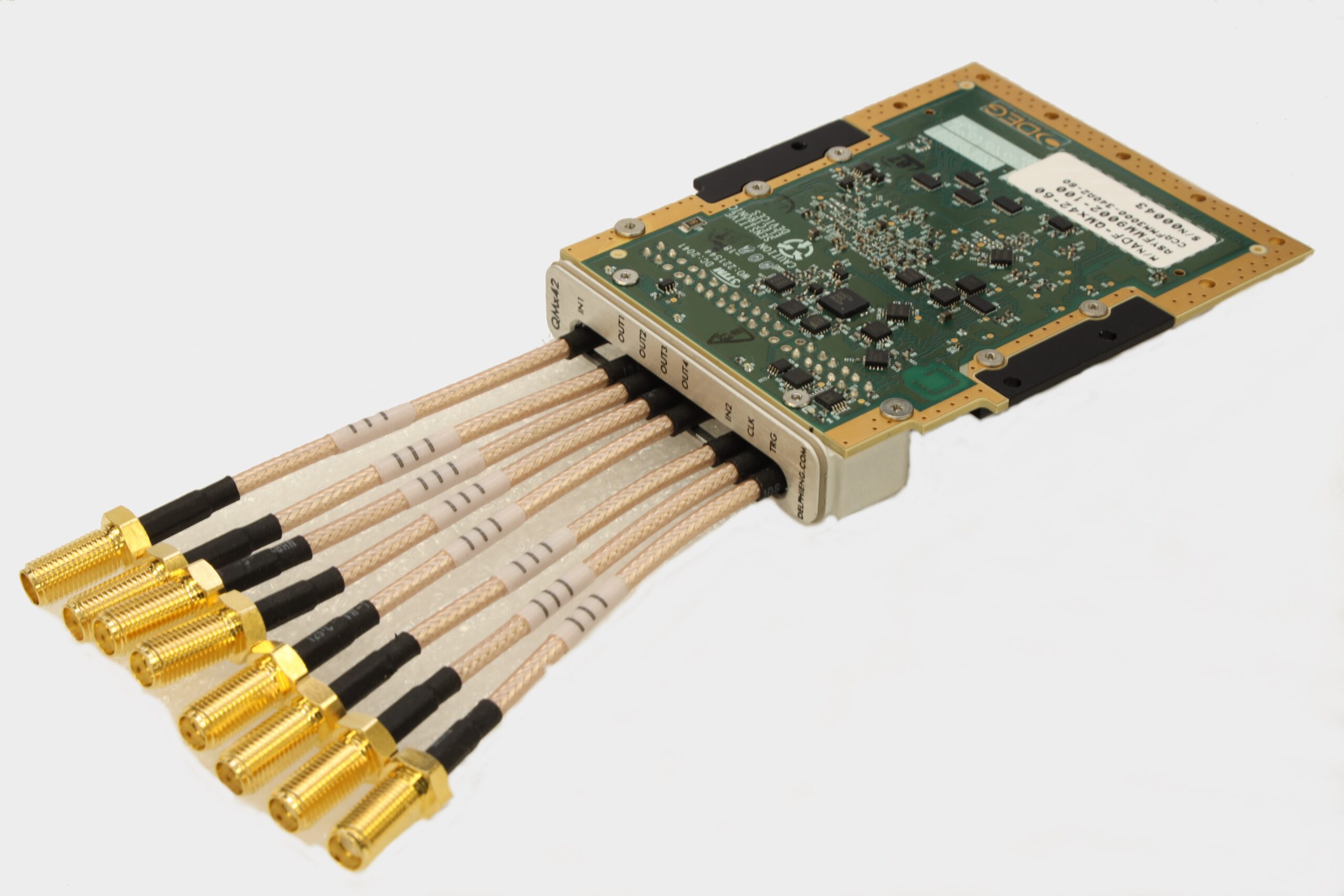

ADF-Q6012

Quad 6 Gsps 12-bit ADC

JESD204C / JESD204B Interface

VITA 57.4 FMC+

- Wide Dynamic Range

- High Channel Density

- Ideal for SWaP-C Sensitive Application

- Designed for AMD UltraScale and UltraScale+ FPGA Carrier Boards

- Multi-Board Channel Alignment Capability

- Built-in Clock Jitter Cleaner

- Configurable digital down conversion (DDC)

- Analog Device part: AD9207

Please fill out form below to download datasheet.

* INDICATES REQUIRED FIELD

The DEG ADF-Q6012 FMC includes four 12-bit, 6 Gsps RF analog-to-digital converters (ADC). The ADF-Q6012 features a 16-lane, 24.75 Gbps JESD204C interface, flexible clocking and triggering options. This ADF-Q6012 leverages two Analog Devices AD9207 MxFE (Mixed Signal Front End) ICs, elevating the technology to a new level of integration.

The AD9207 also has an on-chip clock multiplier, and a digital signal processing (DSP) capability targeted at either wideband or multiband direct from RF applications. The DSP data paths can also be bypassed to allow a direct connection between the converter cores and the JESD204B/C interface.

Flexible & Cost-Effective Solution

By coupling this core architecture with the compact and flexible FMC form factor, DEG has enabled customers to rapidly and cost-effectively build compact and rugged systems of high-speed digitization on a single high-performance FPGA carrier board.

The front panel of the ADF-Q6012 provides seven SMA coaxial connections for the four analog inputs, an external trigger, an external clock or reference, and one signal for board to board channel alignment.